本次技术论坛的演讲主题表明,半导体行业正转向以芯粒(Chiplet)集成为核心的设计理念。在硬件层面,通过2.5D/3D异构集成、创新的低延迟互连技术以及先进的光刻与键合工艺,构建更强大、更灵活的计算系统。在软件层面,开发覆盖全栈的EDA工具、模拟器和编译器,以驾驭多芯粒架构的复杂性。这种软硬件的深度协同,共同推动着AI、高性能计算乃至医疗健康等领域的持续创新。

下表将深理工芯粒集成技术产业创新中心(筹)下设的十个专业实验室的专家演讲主题归入芯粒集成生态系统的不同层面,为读者提供一个理解本次技术盛宴的逻辑框架。

算力核心NPU模拟器和编译器

AI的指数级增长亟需基于芯粒的硬件方案,但若没有复杂的软件栈,硬件将毫无用处。深理工核心软件实验室正在开发从NPU模拟器(ONNXim)到NoC框架和编译器的关键工具,以管理、优化和部署跨多芯粒系统的复杂AI模型,应对软硬件协同设计的核心挑战 。

*NPU Chiplet 芯片模拟

深圳理工大学核心软件实验室的全泰崧和姚洪涛博士指出,NPU本身没有独立的操作系统,它被集成在更大的SoC中,由整个系统的软件栈和操作系统管理 。为了让上层AI应用能够高效地在芯粒硬件上运行,必须建立一个包含驱动、编译器和运行时库的完整软件栈。其实验室正致力于开发这一系列核心软件,其工作涵盖了从高层次模型到底层硬件的全链路模拟与优化。此外,其实验室还开发了精细到flit(流控单元)级别的NoC(片上网络)模拟器,用于优化芯粒间的通信拓扑、路由算法和调度策略,这对于降低多芯粒系统中的数据搬运延迟至关重要 。

Chiplet时代先进封装工艺下的异构集成EDA技术

若没有先进的EDA工具,设计基于芯粒的系统将无从谈起。华大九天展示了其针对2.5D/3D异构集成的全流程解决方案,应对从跨芯片布局规划、自动布线到多物理场(热、电)仿真的挑战,将设计周期从数月显著缩短至数周 。

*华大九天先进封装异构集成方案

华大九天的谈玲燕指出,三维芯片集成是继尺寸微缩和新材料之后的第三条发展路径,而芯粒是其中的关键。然而,芯粒设计带来了巨大的EDA挑战,包括系统分割、高速互连的信号完整性、跨尺度的多物理场仿真以及接口标准化等。华大九天为此提供了名为“Empyrean Storm®”的先进封装解决方案,这是一个一体化的版图平台,旨在替代传统的手工布局,提升效率和数据稳定性。在物理验证方面,其Argus®工具通过创新的全局分析算法,将设计规则检查(DRC)的误报率降低350倍,性能提升5倍,并有效解决了开路真假难辨的行业难题。展望未来,华大九天正在构建完整的3DIC设计全流程,涵盖跨工艺协同设计、协同仿真、异构融合物理验证以及多物理场分析,致力于实现系统技术协同优化(STCO)。

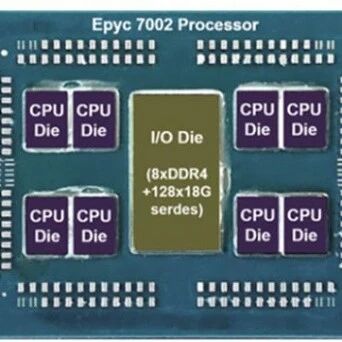

以芯粒集成方式探索高性能RISC-V架构设计

芯粒集成是释放RISC-V在高性能计算领域潜力的关键。通过将功能分解为专用的“计算”、“加速”和“接口”芯粒,这种方法克服了单片设计的局限性,并充分利用RISC-V固有的模块化和可定制性优势,创造出功能强大且可扩展的解决方案 。

*基于芯粒的RISC-V架构分层设计

新紫光集团前沿技术研究院执行院长谢巍博士指出,尽管RISC-V凭借其开源、模块化的特性在嵌入式领域取得了巨大成功,但在向服务器、AI等高性能计算领域迈进时,传统的单片SoC设计遭遇了摩尔定律放缓、良率与成本限制以及功能集成困难等瓶颈 。芯粒技术为此提供了破局之道。报告提出了一种“计算芯粒+加速芯粒+接口芯粒”的分层架构。报告还强调了芯粒间高速互连标准(如UCIe)的重要性,并引用了国内成功研制2Tb/s硅光互连芯粒的案例,证明了高速接口对提升RISC-V整体性能的关键作用 。

揭秘Chiplet互连与现代高性能Soc架构

AI时代的性能扩展本质上是一个互连问题。张博士介绍了HPC(高性能计算)互连技术的演进,论证了低延迟、并行、全双工的总线复制技术——而非交易型SerDes——是NVIDIA B200等芯粒SoC维持UMA(统一内存访问)级性能、避免NUMA(非统一内存访问)瓶颈的关键 。

*芯砺CL-Link D2D vs. Transactional SerDes

深理工芯粒体系结构实验室主任、芯砺智能创始人兼CEO张宏宇博士指出,传统的交易型SerDes因其打包、编码、解码过程引入了巨大延迟(通常大于50ns),无法满足未来高效片间互连的需求。与之相对,芯砺智能(CHIPLITE)提出的CL-Link D2D技术,通过“逐周期”实时总线复制,将片间延迟降低到惊人的5ns以下,为实现真正的低延迟芯粒互连提供了新的范式 。

光互联技术在先进封装中的机遇与挑战

随着电气互连遭遇物理瓶颈,光互连正成为未来数据密集型系统的必然选择。付博士描绘了“铜退光进”的趋势,阐述了光电共封装(CPO)技术如何通过将光子器件直接集成到封装上,来大幅降低功耗和延迟,从而为下一代AI集群提供动力 。

*光电共封装设计核心原则

随着AI算力需求每2-3个月翻一番,计算性能与互连带宽之间的差距日益扩大,铜互连的损耗和距离限制成为主要瓶颈 。南开大学智能光子研究院付孟博博士指出,光互连是解决这一矛盾的关键。不断缩短电互连的距离。这一原则推动了技术形态的演进,从板载光学(OBO)、近封装光学(NPO)最终走向光电共封装(CPO)。CPO将光引擎和交换芯片ASIC封装在同一基板上,相比传统可插拔方案,能效提升4-8倍,带宽密度提升5-10倍,延迟降低10倍 。报告还探讨了实现CPO的关键技术要素,包括先进封装、高密度光互连以及光、电芯片的集成,并对InP、硅光(SiPh)、薄膜铌酸锂(TFLN)等不同材料平台的优劣进行了分析,指出了玻璃基板、氮化硅波导等异质集成方案的机遇与挑战 。

光刻及微纳加工技术促进芯粒集成技术发展

芯粒集成将前端制造的精度带入了后端封装领域。深理工光刻技术及微纳加工实验室主任、中科院微电子所研究员李世光博士阐述了光刻与微纳加工技术在制造TSV(硅通孔)、RDL(重布线层)和微凸块等关键2.5D/3D结构中的核心作用,并强调了基板翘曲、芯片位移等带来的独特挑战,以及对新型、灵活光刻工具的需求。

*Lithography(不同类型的光刻工具)

李博士指出,与传统前端制造不同,先进封装中的光刻面临着一系列独特的难题:首先,基板(如Interposer)的翘曲和形变会降低工艺窗口,使得图形偏离预期位置,对套刻精度构成严峻挑战;其次,在重构RDL重布层的晶圆上,芯片的随机位移(Die Shift)使得传统的掩模光刻难以对准,而无掩模的数字光刻虽然灵活,但面临产能瓶颈;最后,大尺寸面板级封装的兴起,对能够处理大面积、方形基板的新型光刻设备提出了迫切需求。李博士的研究方向聚焦于应对这些挑战的解决方案。随着技术的不断成熟和产能的提升,数字光刻有望在未来逐步取代传统的掩模光刻,从而为芯粒集成技术的发展扫清障碍,开启一个全新的制造范式。

芯粒异构集成封装技术介绍

AI对数据、带宽和功耗的巨大需求正将芯片设计推向单片极限之外。齐力半导体(HChiplet)展示了先进封装,特别是基于芯粒的2.5D/3D集成,如何成为关键的前进路径,它使得超大尺寸芯片成为可能,克服了良率问题,并集成了HBM等异构组件,为下一代AI加速器提供动力 。

*Chiplet化繁为简

齐力半导体的谢建友博士指出,先进封装是应对这些挑战的核心武器。介绍了从传统系统级封装(如MCM-QFN)到先进封装(如Fan-out, 2.5D/3D)的演进。其核心是异构集成(Heterogeneous Integration),即将不同工艺、不同功能的裸片(Die)集成在一起。芯粒技术正是这一理念的体现,它将复杂的SoC分解,允许CPU、内存、I/O等单元采用最适合的工艺分别制造,再通过中介层(Interposer)等技术互连。这种“化繁为简”的设计理念,不仅能大幅提升大芯片的良率,降低成本,还能灵活组合功能,缩短开发周期 。

键合工艺设备:助力先进封装发展的关键力量

先进的封装架构依赖于先进的设备。华封科技(Capcon)强调,高精度键合设备(Die bonder 或贴片设备)是芯片制造的“起重机”,它实现了2.5D/3D和混合键合所需日益增加的互连密度。贴片机的精度和速度是高性能AI芯片制造的赋能者 。

*贴片机是建设复杂芯片最关键最核心设备

华封科技的吕芃浩博士指出在AI时代,算力、功耗和成本是核心制约因素,而摩尔定律的放缓使得先进封装成为提升芯片性能的主动引领力量 。报告的核心论点是,先进封装的本质是不断提升互连密度,而实现这一目标的关键物理支撑,正是贴片设备。报告将贴片设备比作城市建设中的起重机,通过“拾取与放置”(Pick & Place)的方式,将各式各样的芯粒构建成复杂的芯片互联结构 。随着封装技术从倒装焊(Flip Chip)发展到热压键合(TCB),再到混合键合(Hybrid Bonding),对贴片精度的要求也从几十微米提升到亚微米级别。高精度贴片是高性能AI芯片封装的第一道门槛,尤其是在2.5D/3D封装、HBM堆叠等应用中,互连间距不断缩小,对贴片精度提出了极致要求 。作为全球领先的先进封装设备制造商,华封科技不仅在晶圆级封装领域占据鳌头,更在2.5D及颠覆性的板级封装领域具备先发优势,并且是全球率先提供大尺寸板级封装量产设备的厂商。

芯粒集成技术领域的检测设备

芯粒集成的复杂性催生了对新一代智能检测设备的需求。从高分辨率AOI(自动光学检测)晶圆缺陷检测,到先进探针台和高低温测试系统的关键工具,这些设备对于确保多芯片封装的良率、质量和可靠性至关重要 。

*苏州睿萃智能科技的“自动晶圆图形缺陷AOI检测设备”

深理工半导体检测中心实验室主任、新加坡A*STAR光学精密测量技术专家和顾问方仲平博士的报告汇集了多家领先设备商的解决方案,全面展示了芯粒制造链中不可或缺的“眼睛”和“探针”。报告首先介绍了苏州睿萃的晶圆图形缺陷AOIP检测设备,该设备采用明暗场光学系统和AI算法,能够检测划伤、颗粒、隐裂等微小缺陷,并兼容单双面检测 。接着,方博士详细介绍了深圳视觉龙公司,该公司提供从经济型到旗舰型的“龙睿AIoT”视觉平台,将AI大模型、传统视觉与运动控制相结合,推出了MLED AI质检设备和双臂检测机器人等创新产品,旨在解决复杂场景的检测难题 。在可靠性测试方面,成都中冷低温科技提供了覆盖-80℃到+225℃的各类高低温冲击和温控设备,用于芯片的性能验证和失效分析,满足军工和JEDEC等严苛标准 。此外,报告还涵盖了用于失效分析的微区取样仪(SKYannex)、用于内部缺陷检测的超声波观察装置,以及森美协尔(SEMISHARE)提供的从手动到全自动的晶圆探针台,这些设备共同构成了保障芯粒集成产品质量的关键基础设施 。

基于系统级封装的智能算力协同与医疗级算法融合创新应用研究

芯粒技术即将通过“医疗级AI算法定义芯片”重塑创新医疗器械行业。通过系统级封装(SiP)技术集成专用的传感、处理和通信芯粒,晶岚微系统与深理工算力微电子学院正在为实时房颤监测等创新医疗应用联合研发专业芯片,目的是结合多模态医学生理信号分析及以其为基础的闭环调控机制构建从临床需求到芯片实现的闭环系统。

*基于系统级封装的智能算力协同与医疗级算法融合创新

深理工智能医学工程协同创新实验室主任陈秋宝讲解了实验室的宏大愿景:聚焦医学临床、生物医学工程与高性能算力的深度交叉融合。其核心路径是“医疗级AI算法定义芯片”,即通过临床需求反向定义芯片功能,再利用芯粒集成和SiP技术实现。报告以一个“房颤预警芯片”的研发为例,详细阐述了从临床需求调研(实时预警、低干扰、长续航),到数据采集与标注,再到算法设计(基于RR间期变异性),然后进行芯粒架构规划(心电调理芯粒+AI推理芯粒+通信芯粒),最后通过SiP封装、性能测试、设备集成和多中心临床验证的完整闭环流程 。这种模式的价值在于,它将医疗器械的创新从板级系统设计提升到了芯片级,有望在医学影像、可穿戴设备、医疗机器人、诊断监护和治疗设备等领域催生大量创新,最终目标是将植入式医疗设备从“单一功能器械”进化为“可进化的人体协处理器” 。

结语

一个以芯粒(Chiplet)为核心、软硬件深度协同的全新计算时代正加速到来。从底层的光刻、键合工艺,到中层的异构集成与光电互连架构,一系列前沿创新成果的涌现,不仅展示了技术的巨大潜力,更揭示了未来十年半导体产业发展的核心驱动力——构建一个开放、协作、共赢的芯粒新生态。

芯启未来,智创生态