在设计多裸片系统级封装(SiP)时,最关键的决策之一往往也是最早需要做出的决策:系统如何分区。SiP中会包含多少颗裸片?功能将如何在这些裸片之间分配?是采用相对保守的分区方案,仅将系统级芯片(SoC)、I/O控制器和内存等分别集成在独立裸片上?还是转向更激进的芯粒(chiplet)架构,将计算与控制功能分散到多个小型芯粒中?

在做出这些决策时,设计人员必须综合考虑多个因素:功耗、性能和组装成本是否达标;芯粒可获得性、新裸片设计带来的影响,以及与现有系统和软件的兼容性。此外,还需评估设计资源、代工厂,以及封装与测试环节的可用性和能力。

互连技术正是贯穿所有这些考量的核心议题之一。裸片上互连、裸片间连接、裸片至衬底连接及其内部走线,各自属于不同的技术层级,具有独特的机械要求、功耗和时序特性,也对供应链产生了不同影响。

无论在系统设计中采用哪一类互连方式,都将深刻影响最终系统的性能表现和供应链结构。

层次结构

将这些技术视为一个互连层次结构,有助于理解其差异。从裸片内部到PCB板级,每一层的互连速度都逐渐变慢、密度降低、能效下降,同时连接跨度逐步增加。因此,每一层级都适用于特定场景,而并不适合所有用途。

图1:多裸片封装为设计人员提供了多层互连层次。

让我们从最底层开始:裸片内部互连。裸片上多层金属互连的特性已为芯片架构师和设计师所熟知,此处不再赘述。

在同一裸片上,两个相邻模块之间可实现的低延迟、高带宽、低功耗和高连接密度,是互连层级中其他任何层级都无法比拟的。

就速度和能效而言,单裸片SoC仍是最佳选择。但随着工艺逼近物理极限,单片集成已非万能解。如今,越来越多的设计转向多裸片SiP结构。

在许多方面,裸片堆叠是单片SoC的最佳替代方案。这也就引出了互连层级结构的下两个层级:混合键合和微凸块。

面对面

裸片堆叠允许在裸片表面之间建立直接电气连接,从而形成极短的电气通路。结合硅通孔(TSV)技术——通过在裸片中钻孔并贯穿金属层,实现信号从顶部到底部的传输——堆叠多个裸片,可达成高速、相对低功耗的互连。具体堆叠数量取决于工艺能力和供应商支持。

目前主要有两种面对面互连技术。其中,混合键合是最先进、最昂贵且实现难度最高的技术。在此工艺中,一个已完成的裸片会在其互连顶层之上覆盖一层额外的氧化层。

该氧化层可施加于正面或背面。接下来,对氧化物进行光刻掩模并蚀刻,形成直达互连顶层铜接触点的深孔。随后,用铜将这些孔几乎填充至顶部,并对表面进行高精度的平坦化处理。

将两个经过上述处理的表面面对面压合,使其内部填充铜的孔洞精确对齐。两层氧化物表面发生化学键合,在两个裸片之间形成牢固的机械连接。随后对整体结构进行加热,促使铜填充部分膨胀并融合,若工艺控制得当,便可形成可靠的电气连接。该工艺已在晶圆上晶圆(WoW)和晶圆上芯片(CoW)两种工艺中得到验证。

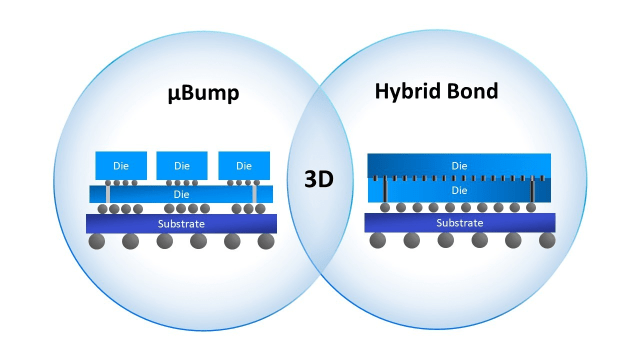

这些混合键合实际上构成了另一个略厚且在某些工艺细节上存在挑战的互连层(见图2右)。因此,从电气特性来看,几乎相当于两个裸片的互连堆叠通过一个共享的顶层实现了合并。该工艺能够实现当今所有方法中最高的连接密度,其中WoW的互连间距可小至400nm,CoW的间距可小至2μm。由于其在延迟、带宽和连接密度方面的表现与裸片内部的上层金属互连相当,因此在裸片之间直接布设芯片级总线、片上网络(NoC),甚至对延迟要求不那么敏感的流水线结构,都成为可行的设计选择。

另一种更为常见的面对面连接技术是使用微凸块(见图2左):在顶层金属的接触点上沉积大量铜柱,通常还会覆盖焊料以提升键合质量。相比混合键合,微凸块对光刻和平面化的要求显著降低。

图2:3D微凸块堆叠(左)添加了一层互连层。3D堆叠(右)还添加了具有不同特性的层。

然而,微凸块的电阻抗比混合键合连接更高,且实际最小间距约为20至40μm,导致单位面积内的连接数量更少。

这些限制虽然降低了堆叠裸片之间可实现的带宽,但尚未严重到完全无法在裸片间布设总线的程度。值得肯定的是,微凸块技术已相当成熟,且在较大间距下对工艺要求较低,为供应链管理和产品生命周期管理提供了更广泛的选择空间。

如果不堆叠呢?

然而,裸片堆叠仍主要用于高带宽存储器(HBM)堆叠,以及大型数据中心CPU和GPU等高端产品。如今大多数SiP设计仍采用2.5D封装:多个裸片并排安装在衬底上。在2.5D架构中,互连情况与裸片堆叠方案不同。

如果衬底是硅中介层,则裸片和中介层之间的连接仍可采用微凸块。但当前中介层制造和组装工艺限制了最小凸块间距约为25µm。

一旦信号穿过微凸块进入中介层,就会遭遇另一个严重瓶颈。中介层上的传播延迟、信号完整性挑战以及信号间的时序偏差,使得在裸片之间运行高速并行总线变得难以实现。因此,高带宽信号通常会被打包、编码并序列化,基于UCIe或HBM等协议,在高速串行通道上传输。这种方式类似于在PCB板间使用PCIe传输数据。

这些通道的数据速率最高可达每条走线32GT/s,能耗可低至0.25pJ/bit。但随着传输距离的增加,速度会下降,能耗也会增加。

最快的UCIe版本规定最大走线长度为2mm——裸片必须几乎紧贴,且通道的微凸块需布置在裸片最边缘。更宽松的UCIe版本可支持长达25mm的通路,但需增大凸块间距,且数据速率明显降低。

通过将16到64条走线组成一个集群,UCIe可在短距离内实现裸片间非常高的传输速率。但这需要付出延迟代价。数据必须经过打包、编码、并串转换、跨衬底传输、数据恢复、纠错以及串并转换,才能到达目标裸片。

系统设计人员必须确保裸片间的高带宽连接对延迟不敏感。流式数据传输类应用表现良好,但需要在严格时间预算内将随机量数据传输到随机位置的应用则可能遇到瓶颈。高速串行通道不是系统总线。

当然,除了硅中介层以外,还有其他衬底技术。有机衬底由于成本更低,供应链更成熟,广泛用于主流封装。但它在凸块间距(通常使用类似PCB的C4凸块)和单条走线最大速率方面均有所牺牲。

它多采用PCIe等高速串行标准,而非UCIe,或依赖专有收发器技术来部分弥补数据速率损失。玻璃衬底的使用也正在探索中。其架构情况类似,间距、比特率和功耗介于硅和有机材料之间。

全面规划

决定采用多裸片SiP架构,意味着必须将互连层级结构纳入系统设计的核心考量。关于系统分区——哪些功能应放在哪个裸片上——的决策,必须充分评估各层级互连在带宽、延迟和功耗方面的特性。

同时,还必须考虑现实因素,包括设计团队的专业能力、工艺成本以及供应可获得性。

因此,从项目早期阶段就应让专家参与分区决策。这些专家需具备扎实的技术知识,与晶圆厂及中介层制造商保持紧密合作,并熟悉在裸片就绪后能够承接SiP封装与测试的厂商。

这种专业能力可以由企业内部自主培养,也可借助值得信赖的设计合作伙伴来获取。然而,在当前快速演进的SiP设计与先进封装领域,这类专业能力必不可少。

作者:智原科技设计方法部部长陈望矜博士

(责编:Franklin)

THE END

关注“电子工程专辑”加小编微信

现已开放地区群,请发送消息【深圳】【上海】【北京】【成都】【西安】到公众号