做 PCB 设计的朋友,肯定见过有些信号线上串着个电阻吧?这不起眼的小零件,到底是干嘛的?今天就用最直白的话给你讲清楚,看完你就懂了~

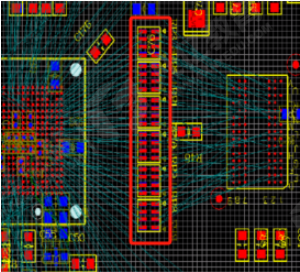

就拿常见的例子来说,CPU 和 DDR 颗粒连接的数据线,每根线上都串了个电阻。这电阻的核心作用,就是让信号更 “听话”,防止它乱跑 —— 专业点说叫 “阻抗匹配”,能避免信号反射。

光说原理太枯燥,咱们用仿真软件实际看看效果,一目了然~

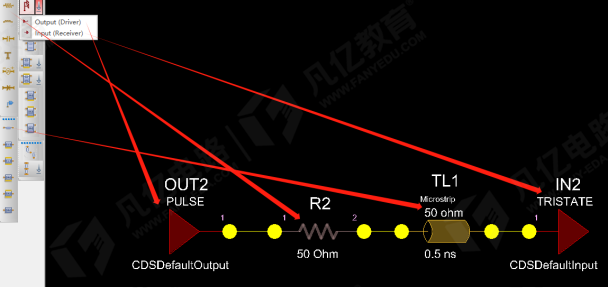

第一步,先搭建一个链路模型,把传输线的阻抗设为常用的 50 欧姆,再把发送端(tx)和接收端(rx)换成 1.8V 的高速模型,这样才能模拟真实的信号传输场景。

我们选了 6 种电阻值来测试:0 欧姆、10 欧姆、20 欧姆、30 欧姆、40 欧姆、50 欧姆,专门看看它们对信号反射的影响。

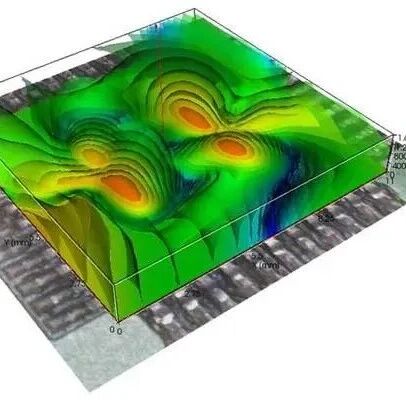

仿真结果一出来,差别立马就显出来了:

没串电阻(0 欧姆)时,信号 “冲得太猛”,过冲特别严重;

换成 10 欧姆、20 欧姆,过冲慢慢变小,波形好看多了;

到 30 欧姆的时候,波形最稳,既没有过冲也没有拖沓,信号质量最好;

可到 40 欧姆、50 欧姆时,信号上升变缓,还出现了欠冲,反而不太理想。

记住,电阻不是越大越好,也不是越小越好!关键是让 “发送端的内阻 + 串联电阻的阻值” 等于或接近传输线的阻抗(比如前面的 50 欧姆),这样才能消除反射。

实际设计中,一般先试试 22-30 欧姆,具体数值最好通过仿真验证,或者后期调试时换不同阻值试试,直到信号达标。

小知识:现在的 DDR 咋没这电阻了?

现在的 DDR 用了 ODT 技术,把电阻集成到芯片内部了,而且还能调!不过要注意,ODT 只针对数据线,地址线、控制线、时钟线这些如果不处理,还是可能出现信号反射。

另外,串联电阻一定要尽量靠近发送端放,放太远了就起不到改善信号的作用啦~

END

点击了解活动详情

点击了解活动详情往期精选:

请点下【♡】给小编加鸡腿