Chip Basic Information

01. 芯片简介

Block Parsing

02. 分块解析

(一)ADC 模块设计

采样保持电路:采用高速电容式采样结构,采样时间仅为 50ns,可有效减少信号采样过程中的失真,确保在高频信号采集场景下的稳定性; DAC 反馈网络:内置 12 位 R-2R 梯形电阻网络,该网络通过精准匹配的电阻元件实现低非线性误差,配合低温漂运算放大器,使 ADC 的积分非线性误差(INL)控制在 ±1LSB 以内; 时钟与控制单元:支持外部时钟输入(最高 50MHz)与内部时钟模式,时钟抖动控制在 10ps 以下,避免时钟噪声对转换精度的干扰。

(二)DAC 模块设计

电流源阵列:采用 PMOS 管电流源,通过版图优化实现电流匹配度误差小于 0.1%,确保 DAC 输出的线性度; 输出缓冲电路:集成高带宽运算放大器(单位增益带宽为 100MHz),输出电压建立时间仅为 1μs,带负载能力可达 500Ω,可直接驱动外部执行机构; 失调校准机制:内置数字校准寄存器,用户可通过软件配置补偿 DAC 的零点漂移,在 - 40℃至 + 85℃温度范围内,失调电压漂移控制在 ±5μV/℃以内。

(三)通信与控制模块

SPI 接口:支持标准 SPI、QSPI 等多种协议模式,采用 16 位数据帧结构(8 位命令 + 8 位数据),通过 CRC 校验位减少传输错误,在 50MHz 时钟频率下,数据传输速率可达 50Mbps; I2C 接口:支持 100kHz(标准模式)与 400kHz(快速模式),具备从地址自动识别功能,可同时挂载 16 个从设备,适用于多芯片协同工作场景; 寄存器映射机制:芯片内置 32 个可配置寄存器,涵盖通道使能、增益设置、故障检测等功能,寄存器读写采用 “写使能 - 数据写入 - 校验” 三步流程,防止误操作导致的参数配置错误。

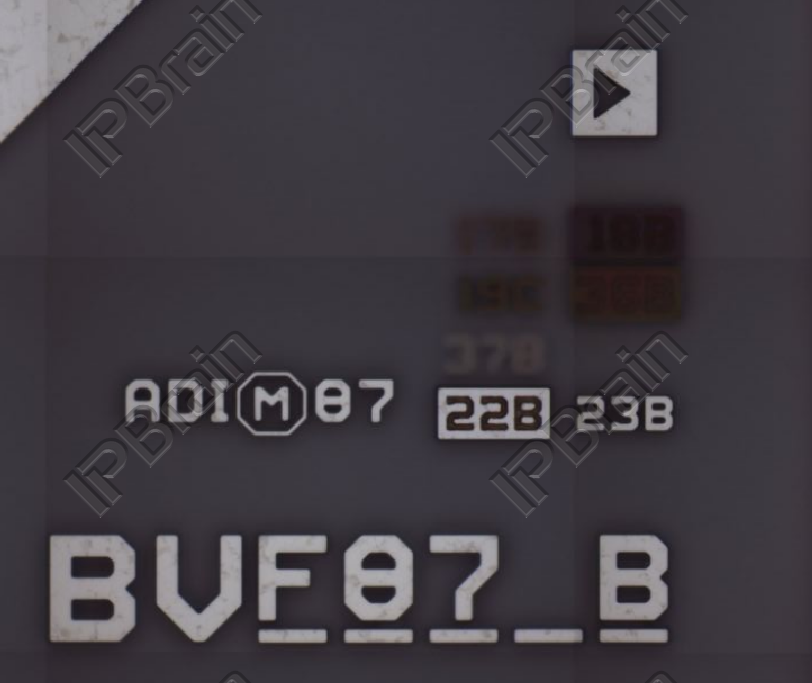

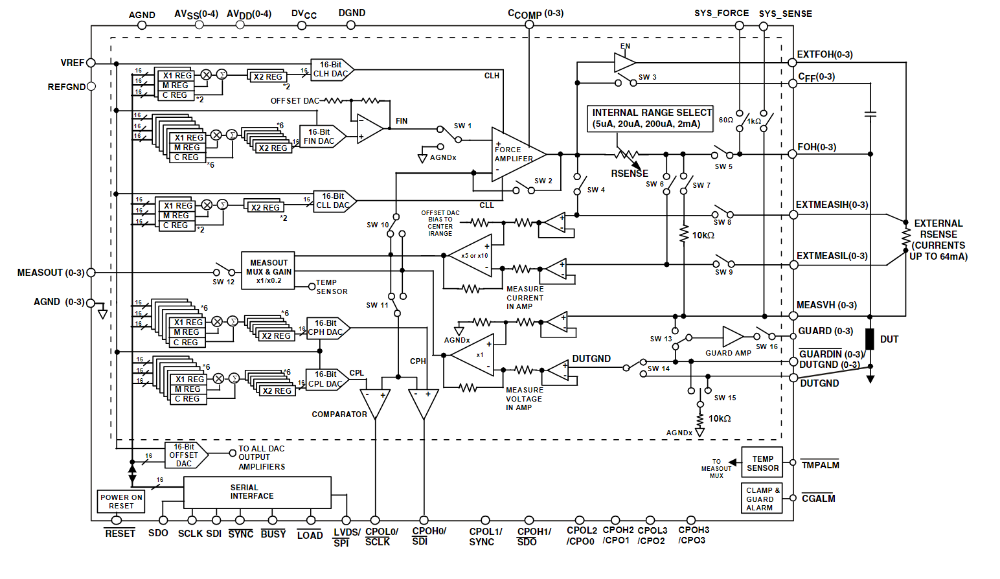

Chip Detail Diagram

03. 芯片细节图像

器件图像

Application Scenario

04. 实际应用

高端工业控制领域:

智能医疗领域:

精密仪器领域:

往期推荐 >