从3μm到超越2nm的A16,每一页都是量产实力的注脚。

当全球芯片行业沉迷于PPT参数竞赛时,台积电(TSMC)一直在官网上用毫无水分技术资料,用硬核数据揭示了半导体霸主最深的护城河,并宣告了真正的游戏规则——技术不是拿来讲的,是拿来造的。

以量产能力定义技术话语权

台积电完整披露从3μm(1987年)到A16(未来节点)的55年技术演进。

但最震撼的并非尺寸微缩,而是台积电独创的「平台化作战体系」:

·模块化技术矩阵:同一节点裂变N个版本

5nm不只N5基础款,更衍生N5P(性能增强)、N4X(高性能计算)、N5A(车规级)等场景化变体;3nm家族更扩展为N3E/N3X/N3A四重奏,将单一工艺榨出极限价值。

·物理与系统双突破

A16技术引入NanoSheet晶体管+背向供电(SPR),在维持布局灵活性的同时提升1.1倍密度;N2工艺集成低阻RDL布线和高性能MiM电容,实现从晶体管到系统层级的全栈优化。

量产即王权:改写行业生存法则

台积电用三组数据定义新定律——「谁能稳定量产,谁就拥有解释权」:

1.N3全球首量产:2022年投产即实现「高产能量产」,非实验室样品

2.N2提前锁胜:客户IP设计完成流片,量产节奏领先对手1年以上

3.A14/A16超预期:良率表现超前路线图,相同功耗下速度提升15%

底层哲学:三十年磨一剑的「笨功夫」

台积电公开的技术节点资料的本质,是台积电技术哲学的实体化:

·自研信仰:从拒绝IDM联合开发(0.13μm时代),到斥资千亿建研发中心

·生态捆绑:客户流片与工艺研发同步推进,N2投产前已导入客户设计

·拒绝奇迹:7nm到5nm的EUV过渡、3nmFinFET量产,全靠无数次验证

启示录:中国大陆的芯片该追什么?

当行业苦追5nm时,台积电已在冲刺A16。差距不在单点技术,而在「产业组织方式」:

“我们比的不是节点数字,而是整个系统能力”

这揭示的,是研发体系、工艺-设计协同、客户生态的三位一体战争。

台积电的技术节点编年史

【内容目录】

从起点出发,理解技术节点

摩尔定律:指引行业的灯塔

A14技术

A16技术

2nm技术

3nm技术

5nm技术

7nm技术

16/12nm技术

20nm技术

22nm技术

28nm技术

40 nm技术

65nm技术

90nm技术

0.13µm技术

0.18µm技术

3μm技术

引言

在动态发展的电子领域,“技术节点”已成为核心概念,特指定义硅芯片尺寸与能力的半导体制造工艺集合。历史上,该领域的快速发展被摩尔定律精辟概括。该定律由英特尔联合创始人戈登·摩尔于1965年提出,观察到微芯片上的晶体管数量约每两年翻倍,推动算力呈指数级增长的同时成本减半。通过回顾半导体从早期阶段到当今尖端节点的演进历程,我们既要肯定已实现的技术壮举,也需预见未来的突破性创新。

从起点出发,理解技术节点

技术节点的编年史始于1960年代半导体产业诞生之初。“节点”指代特定代际的半导体制造工艺,传统上表示芯片可制造的最小特征尺寸。该特征最初是晶体管的栅极长度,始于微米级(1微米、800nm、600nm...),现已进入以纳米(nm)为单位的时代——如7nm、5nm乃至3nm节点。

TSMC始终坚持构建强大的自主研发能力。作为全球半导体技术领导者,TSMC提供最先进、最全面的专业晶圆代工工艺组合。

图1:台积电工艺节点编年史

摩尔定律:指引行业的灯塔

数十年来,摩尔定律不仅是观察结论,更是引导半导体产业自我实现的预言。晶体管密度每两年翻倍,持续推动电子设备在性能、能效和成本效益上的提升——从简易计算器到复杂超级计算机。这是人类智慧的证明,彰显对技术进步的不懈追求。然而,随着技术节点持续微缩,我们正逼近材料物理极限与量子力学定律的边界。挑战包括过热、功耗泄漏,以及当元件达到原子尺度时电子出现不可预测运动的量子隧穿效应。

A14技术

A14技术是TSMC通过尺寸微缩实现全节点功耗、性能与面积优化的下一代尖端逻辑工艺。

A14旨在通过更高算力与能效推动AI转型,同时有望通过增强智能手机板载AI能力使设备更智能。A14开发进展顺利,良率表现超前于计划。

相较于TSMC业界领先的N2工艺:

•相同功耗下速度提升高达15%

•相同速度下功耗降低高达30%

•逻辑密度增加超20%

依托纳米片晶体管设计-技术协同优化(DTCO)经验,TSMC正在将其TSMC NanoFlex™标准单元架构升级至NanoFlex™ Pro,实现更高性能、能效与设计灵活性。

A16技术

TSMC的A16™技术整合领先的纳米片晶体管与创新的超级电源轨(SPR)解决方案,带来显著改进的逻辑密度和性能。

SPR通过将正面布线资源专用于信号传输来提高逻辑密度和性能。它还显著降低IR压降,提升供电效率。最重要的是,我们新颖的背接触方案在保持栅极密度、布局面积与器件宽度灵活性的同时,实现业界首创的最佳密度与最佳性能。

相较于TSMC的N2P工艺,A16在相同Vdd(正电源电压)下将提速8-10%,相同速度下降低功耗15-20%,芯片密度最高达1.10倍,特别适用于具有复杂信号布线和密集供电网络的高性能计算(HPC)产品。

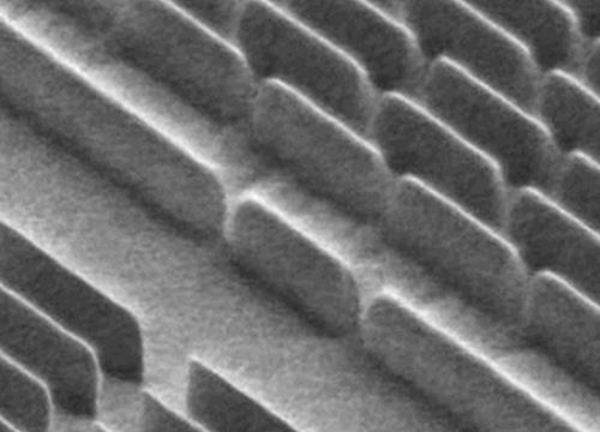

2nm技术

TSMC的2nm(N2)技术开发按计划推进且进展良好。N2技术采用第一代纳米片晶体管技术,在性能与功耗上实现全节点突破。

主要客户已完成2nm IP设计并启动硅验证。TSMC还开发了低阻再分布层(RDL)和超高性能金属-绝缘体-金属(MiM)电容器以进一步提升性能。

TSMC N2技术在推出时将成为半导体行业密度与能效最先进的工艺。凭借领先的纳米片晶体管结构,N2将提供全节点性能与功耗优势,满足日益增长的节能计算需求。通过持续增强策略,N2及其衍生工艺将进一步延续TSMC的技术领导地位。

图2:台积电Fab 20,2nm节点的主要生产基地

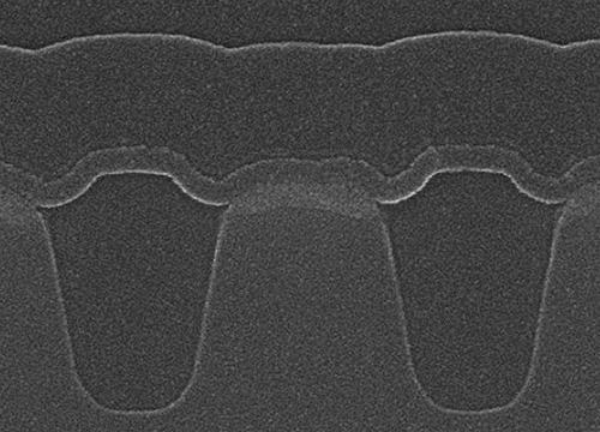

3nm技术

2022年,TSMC成为首家将3nm鳍式场效应晶体管(FinFET)技术(N3)投入量产的晶圆厂。

N3技术是业界最先进的工艺技术,提供最佳性能、功耗与面积。它较5nm代际实现全节点跨越。继N3后,TSMC推出N3增强型(N3E)和N3P工艺以优化功耗、性能与密度。

公司持续扩展3nm技术家族以满足多样化客户需求,包括:为HPC应用定制的N3X、以更优性价比支持价值型产品的N3C,以及面向汽车应用的N3A。

5nm技术

2020年,TSMC成为首家将5nm鳍式场效应晶体管(FinFET)技术(N5)投入量产的晶圆厂,并支持客户在智能手机和高性能计算(HPC)应用中的创新。TSMC的N5技术是公司第二代采用EUV光刻的技术,并取得了与其前身N7+工艺相同的成功。

TSMC持续扩展其5nm技术家族,以满足多样化客户需求。这些包括N5P、N4P和N4C,它们提供更好的功耗、性能、密度和更具成本效益的优势;N4X,专为HPC应用定制的工艺;以及用于汽车应用的N5A。

N5、N5P、N4P、N4C工艺已进入量产,并表现出优异的良率。

图3:台积电Fab 18,3nm和5nm节点的主要生产基地

7nm技术

2018年,TSMC成为首家启动7nm鳍式场效应晶体管(FinFET)技术(N7)量产的晶圆厂。

N7技术是TSMC量产速度最快的技术之一,为移动计算应用和高性能计算(HPC)组件提供优化的制造工艺。此外,7nm FinFET增强型(N7+)工艺于2019年进入量产,是代工行业中首个商用EUV光刻技术。多年来,HPC和5G产品已基于N7和N7+为客户构建。自2021年起,N7和N7+扩展至消费电子和汽车电子产品制造。

2019年,TSMC通过推出6nm(N6)技术进一步增强其行业领先的7nm技术。自2020年进入量产以来,它已被广泛应用于智能手机、HPC和数字消费电子(DCE)产品。N6e®、N6超低功耗(ULP)技术的工艺设计套件(PDK)于2023年完成,该技术于2024年启动生产。

16/12nm技术

2013年,TSMC成为首家开始16nm鳍式场效应晶体管(FinFET)技术风险生产的晶圆厂,并于2014年首家交付全功能16nm FinFET客户网络处理器。

TSMC还推出更具成本效益的16nm FinFET紧凑型(16FFC)技术,于2016年投产。该工艺通过同时结合光学微缩和工艺简化,最大化晶粒成本缩放。12nm FinFET紧凑增强型(12FFC+)技术进一步提升栅极密度、速度和功耗,并于2017年投产。它作为N12e®技术平台的基础,提供超低泄漏器件、低Vdd解决方案、RF模型、模拟增强和eNVM(磁性随机存取存储器,MRAM/电阻式随机存取存储器,RRAM)。

TSMC的16/12nm工艺在业界16/14nm方案中提供最佳性能。相较于TSMC的20nm SoC工艺,它在相同速度下提速50%并降低功耗60%。TSMC的16/12nm工艺为下一代高端移动计算、边缘人工智能物联网(包括微控制器单元MCU、可穿戴设备、高速接口产品、视觉AI、语音AI、超低功耗产品、存储控制器和医疗应用等)、数字消费和汽车电子产品应用提供卓越的性能和功耗优势。

20nm技术

2014年,TSMC使用其创新的双图案化技术成为全球首家启动20nm量产的半导体公司,并在同年创下TSMC最快节点爬坡纪录。

20nm技术因采用高能效晶体管和互连以及世界领先的双图案化技术,提供比先前技术节点更好的密度和功耗价值。

22nm技术

22nm超低功耗(22ULP)工艺技术源自TSMC行业领先的28nm技术。它提供增强的性能和成本效益,适用于图像处理、数字电视(DTV)、机顶盒(STB)、智能手机和消费电子等应用。

22nm超低泄漏(22ULL)工艺技术在22ULP基础上,通过整合超低泄漏(ULL)组件和ULL静态随机存取存储器(SRAM)进一步降低功耗。这使其成为支持物联网和可穿戴相关产品低功耗需求的理想选择,例如智能手表、真无线立体声(TWS)、智慧城市、照明和工业4.0等,并被广泛采用。

28nm技术

2011年,TSMC成为首家提供28nm通用工艺技术的晶圆厂。此后,TSMC持续扩展其28nm技术产品,并提供代工行业最全面的28nm工艺组合,以支持客户交付性能更好、能效更高且更环保的产品。

TSMC的28nm工艺技术具有高性能和低功耗优势。该技术支持广泛应用,包括智能手机5G RF收发器、毫米波和汽车雷达、消费电子、物联网(IoT)等。针对主流智能手机和消费应用,TSMC为客户提供广泛的28nm逻辑工艺技术,包括28nm高性能紧凑型(28HPC)、28nm高性能紧凑增强型(28HPC+)和全面的IP,以满足客户对高性能和低功耗芯片的需求。

为支持客户在物联网领域的创新,TSMC不仅为客户提供坚实的28nm逻辑技术,还构建了领先、完整且高度集成的超低功耗(ULP)技术平台。包括28nm ULP在内的技术已被各类物联网片上系统(SoC)和电池供电产品广泛采用,以延长电池寿命。

此外,TSMC在28nm上提供一系列具有竞争力的汽车级专业工艺技术,包括嵌入式闪存、电阻式随机存取存储器(RRAM)、毫米波(mmWave)RF和超低泄漏器件。

40 nm技术

2008年,TSMC引领晶圆代工行业,使用40nm工艺技术为多个客户启动多种产品量产。40nm工艺集成193nm浸没式光刻技术和超低介电常数连接材料,提升芯片性能同时降低功耗。该工艺还创下业界最小SRAM(0.242µm²)和宏尺寸记录。

除40nm通用型(GP)和低功耗(LP)工艺外,TSMC多样化其40nm工艺以满足更广泛需求,包括40nm增强LP和40nm超低功耗(ULP)工艺。

40nm通用型(GP)针对高性能应用:中央处理器(CPU)、图形处理器、游戏主机、网络、FPGA和硬盘驱动器。40nm低功耗(LP)和增强LP针对智能手机、数字电视(DTV)、机顶盒(STB)、游戏和无线连接应用。40nm超低功耗(ULP)适用于物联网和可穿戴设备。

如今,40nm技术平台已扩展至包含专业工艺技术,包括射频(RF)、嵌入式闪存、BCD和绝缘体上硅(SOI),以拓宽产品应用,例如采用RF技术的5G毫米波前端模块(FEM)设计、采用BCD技术的电源开关,以及采用嵌入式闪存技术的微控制器(MCU)。

65nm技术

2005年,TSMC成为首家开始65nm风险生产的晶圆厂,次年通过产品认证。公司还推出代工行业首个65nm低功耗(LP)工艺以满足客户需求。

继65nm LP工艺后,TSMC快速推出广泛工艺组合,包括通用型(GP)、混合信号/射频(MS/RF)、多次可编程非易失性存储器(MNVM)、嵌入式闪存(eFlash)、高压(HV)、电源管理(BCD)和MEMS工艺。65/55nm技术面向移动设备、计算机、汽车电子、物联网和智能穿戴等广泛应用。

TSMC 65/55nm技术是公司第三代采用铜互连和低介电质材料的半导体工艺。该技术支持的标准单元栅极密度是TSMC 90nm工艺的两倍,通过创新电源管理技术提供更好集成度、芯片性能和显著降低的功耗。

90nm技术

TSMC成为首家使用浸没式光刻技术生产全功能90nm芯片的半导体公司。公司于2004年12月在SEMICON Japan宣布了此成就。

TSMC创新的浸没式光刻采用193nm光刻水介质扫描仪(而非传统157nm干式扫描仪),为全球半导体行业设定了新的扫描仪规格。这一进展强化了TSMC的技术领导地位,助力半导体行业克服推动摩尔定律的挑战,从而驱动工艺技术进步。

0.13µm技术

TSMC推出半导体行业首个0.13µm低介电常数铜系统级芯片(SoC)工艺技术。公司坚持构建自主研发能力,并通过早期关键决策促成此成功——当时拒绝了知名IDM(集成器件制造商)的联合开发邀请。TSMC将研发团队设于新竹总部,先于IDM和其他代工厂成功开发该技术。此成就不仅标志台湾具备先进技术开发能力,更成为台湾半导体产业发展的基石。

TSMC的0.13µm SoC低介电常数铜技术集成多个世界级SoC CMOS晶体管工艺平台、超小型SRAM存储器(2.43-1.87平方µm)、全球最新193nm光刻技术以及全球首款八层低介电常数(k≤2.9)铜布线。如今,它广泛应用于消费电子、计算机、移动计算、汽车电子、物联网和智能穿戴设备。

0.18µm技术

TSMC的0.18μm逻辑技术是半导体制造的里程碑,至今为广泛应用提供可靠且成熟的解决方案。该成熟工艺节点在性能、成本和可靠性间实现优异平衡,成为消费电子、通信、汽车系统和工业设备的首选。

0.18μm技术的关键优势之一是其灵活性。它支持1.8V至5V多电压等级,以适应多样化的器件需求。该工艺无缝集成数字与模拟组件,尤其适合混合信号设计。其满足高压电路和射频(RF)设计等专业应用的能力进一步增强了通用性。

作为成熟工艺,TSMC 0.18μm技术凭借出色的生产良率、低制造成本和稳健的设计生态系统,尤其在无需尖端微缩的产品中提供可靠性和经济性。相较于更先进节点,它以更低成本实现强劲性能,是无需极致微缩设备的实用选择。凭借多年生产历史,0.18μm节点以稳定可靠的性能著称,非常适合汽车和工业系统等长生命周期应用。

TSMC为0.18μm节点提供广泛的设计库、工艺设计套件(PDK)和知识产权(IP)解决方案,以简化设计流程并加速上市时间。

TSMC的0.18μm逻辑技术是需可靠性能与设计灵活性的应用的通用经济解决方案。其支持数字与模拟集成的能力,以及高压和射频兼容性等专业特性,确保了在各行业的持续价值。

3μm技术

TSMC自1987年成立以来始终坚持“自主研发”战略,为公司带来显著竞争优势。

TSMC创始时从台湾工业技术研究院引进2μm和3.5μm技术,但为飞利浦(荷兰)定制开发了3.0μm技术。仅一年后,TSMC于1988年成功自主开发1.5μm技术。后续持续成功开发1.2μm、1.0μm、0.8μm、0.6μm、0.5μm、0.3μm及0.25μm工艺。

1999年,TSMC发布全球首个0.18μm低功耗工艺技术。此后,TSMC创下多项纪录,以从0.13μm、90nm、65nm、40nm、28nm、20nm、16/12nm直至当今最先进10nm与7nm工艺的持续微缩技术引领行业。

凭借“自主研发”战略及持续研发投入,TSMC作为半导体技术领导者,助力全球企业释放集成电路(IC)创新潜力。

*文章编译来源:

半导体产业报告/ 《技术的尽头,不是炫技,而是量产》

芯启未来,智创生态