公众号记得加星标⭐️,第一时间看推送不会错过。

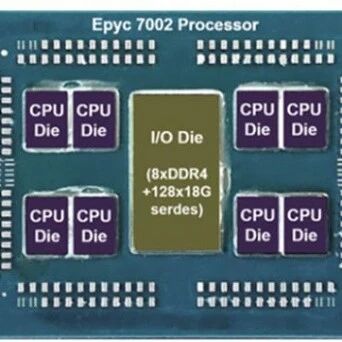

Chiplet是一种满足持续增长的计算能力和 I/O 带宽需求的方法,它将 SoC 功能拆分成更小的异构或同构芯片(称为芯片集),并将这些Chiplet集成到单个系统级封装 (SIP) 中,其中总硅片尺寸可能超过单个 SoC 的光罩尺寸。SIP 不仅包含传统的封装基板,还可能包含允许更高布线密度的中间中介层,从而能够在单个标准或高级封装中提升功能性和集成度。

本文将深入探讨系统设计人员面临的一些关键Chiplet设计和集成问题及决策。

系统分区

设计团队需要考虑的首要问题是,设计中将包含哪些功能块和功能,以及如何将这些功能划分到不同的芯片组中。此外,设计人员还需要选择每个功能块最高效的半导体工艺节点。常见的高阶细分方案可能是将计算芯片、IO 芯片和存储功能划分到不同的芯片组中。接下来,需要根据工艺节点选择和芯片组划分,权衡延迟、带宽和功耗。

流程节点选择

在最新的工艺节点中,AI 加速器中的计算芯片可能是优化性能和功耗的理想选择,但在该节点中实现缓存可能并不理想。缓存可能位于同一芯片上,但 SRAM 在最新节点上的扩展程度可能不如逻辑芯片,因此在成本较低的节点上实现 SRAM 会更高效。此外,通过 2.5D 芯片到芯片接口进行片外延迟要求并不合适。一种选择是 3D 实现,其中计算芯片位于最新节点 N 上,SRAM 和 IO 位于节点 N-1 或 N-2 上。一个例子是带有第二代 3D V-Cache 的 AMD Ryzen7000X3D 处理器,它集成了 3D 堆叠计算和 SRAM 内存,如 AMD 分享新款第二代 3D V-Cache 芯片细节(高达 2.5 TB/s)中所示。

对于模拟功能或 IO 接口功能(例如 PCIe 或以太网),可能对延迟有更高的容忍度,最好将其实现在单独的芯片组中,并通过 UCIe 接口连接到主芯片。为了节省成本,主芯片组可以采用较旧的工艺节点。

芯片间连接考虑因素

UCIe 已成为芯片组之间 die-to-die 连接的实际标准,但选择 UCIe 配置需要考虑诸多因素。设计人员需要根据芯片组的工作负载了解带宽需求。这可能包括主频带数据的带宽,也包括用于控制和管理的侧信道数据的带宽。以 AI 服务器 IO 芯片组应用为例,UCIe 带宽需求与以太网、UALink 或 PCIe 等接口 IP 相关。

设计人员有多种选择,包括每条通道的数据速率以及是否使用具有更长距离的有机基板(UCIe 标准)或使用最小的滩涂和具有最小凸块间距的先进封装(UCIe 先进)。还需要在数据速率(范围从 16G 到 64G)和需要多少条通道才能满足芯片滩涂约束之间进行权衡。可用的滩涂可能会根据接口 IP PHY 布局而变化。根据芯片组的目标尺寸和/或长宽比,设计人员可以选择将 PHY 排列在芯片边缘的单行中。另一种选择是将 PHY 双层堆叠成列,这样滩涂就会减半,但代价是 PHY 区域深度减小。

大多数 UCIe 应用都使用流式传输接口。设计人员必须确定从 UCIe 流式传输到接口 IP 的桥接器。选择可以包括 AXI、ARM CXS 或即将推出的标准(例如 PXS)。可能需要考虑如何将数据打包到可用资源中而不浪费带宽、执行时钟交叉功能,以及决定数据是直接从 UCIe 点对点传输到接口 IP 还是传输到中间片上网络 (NOC),以便在芯片内部提供更灵活的连接。

先进封装带来新的能力和挑战

如今,人们对封装技术的关注从未如此强烈。这些进步带来了巨大的机遇,但在为多芯片设计设计单个或多个芯片时,也带来了更多挑战。

设计人员需要决定如何在多裸片设计中互连芯片。与包含中介层或带硅桥的中介层的2.5D架构相比,有机基板的成本更低,设计进度更快。对于更高级的用例,可能需要中间中介层来满足所需的互连密度以及电源/接地和信号路径。一旦选定中介层,就必须选择成熟的硅中介层、较新的有机基板RDL中介层或带硅桥的RDL中介层,以根据需要提供更密集的互连。硅中介层是成熟的技术,但随着尺寸增大,成本也会随之增加,并且由于脆性原因,其尺寸受到限制。RDL中介层旨在降低成本并提供更大的尺寸,以集成更大的系统和更多的硅含量。

在所有情况下,设计人员都面临着新的挑战,包括机械尺寸、信号完整性和电源完整性分析、单个芯片的热分析以及它们之间的相互作用。为了满足不同芯片、封装和测试的要求,凸块规划和晶圆探针的放置也变得更加复杂。即使在同一种基板或中介层中,凸块间距也可能存在差异,基板的典型值在 110 至 150 微米之间,中介层上使用的微凸块间距在 25 至 55 微米之间。如果添加 3D 芯片堆叠,差异会更大,如图 1 所示。

封装挑战的另一部分涉及测试规划,包括对芯片进行晶圆探针访问以提供已知良好的芯片(KGD),使用 IEEE 1838 协议和多芯片测试服务器来访问可能无法直接从外部引脚访问的芯片。

安全设计与验证

IP 集成带来了一些挑战,包括与互操作性、验证和安全性相关的问题。

一旦设计人员在异构或同构芯片组之间实现了系统分区,设计安全性方面就会出现新的考量。多芯片设计带来了更广泛的攻击范围,需要防范。首要问题是提供认证功能来验证每个芯片组。然后,根据最终应用,设计人员可能需要提供信任根来处理敏感数据,并可能在系统之间传递密钥以提供数据加密服务。设计人员还可以考虑安全启动流程,以防止硬件和固件级别的外部篡改。设计人员还必须考虑保护跨关键接口(例如 PCIe 和 CXL 完整性和数据加密 (IDE)、DDR 和 LPDDR 内联内存加密 (IME) 以及以太网 MACsec 功能)传输的数据。另一个选择是支持 ARM 机密计算架构 (CCA)。

系统级仿真、模拟和原型设计是开发流程中至关重要的步骤,旨在确保功能和性能,从而一次性交付成功的芯片。协同设计工作应涵盖芯片、软件和系统组件,以实现最佳集成度和效率,让设计人员能够在芯片可用之前开发软件。

由此可见,从构思到多裸片设计,需要考虑诸多因素并积累丰富的经验。

参考链接

https://semiengineering.com/chiplet-design-considerations/

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

END

今天是《半导体行业观察》为您分享的第4146期内容,欢迎关注。

推荐阅读

加星标⭐️第一时间看推送,小号防走丢